1. Wprowadzenie

Oscylatorów kwarcowych generują bardzo stabilne sygnały zegarowe, które są niezbędne w niemal wszystkich układach elektronicznych – od prostych układów mikrokontrolerów po systemy szybkiej transmisji danych.

Sygnał wyjściowy oscylatora musi być kompatybilny z następującą rodziną logiczną lub interfejsem. Na przestrzeni dziesięcioleci rozwinęły się różne standardy wyjściowe, dostosowane do wymagań swoich czasów i zastosowań.

W dokumencie tym zawarto kompleksowy przegląd siedmiu najczęściej spotykanych typów sygnału wyjściowego w oscylatorach kwarcowych: CMOS, TTL, Clipped Sine Wave, Sine, LVPECL, LVDS i HCSL.

Dla każdego typu omówiono rozwój historyczny, właściwości elektryczne, typowy kształt sygnału oraz preferowane obszary zastosowań.

2. Rozwój historyczny

Rozwój typów sygnałów wyjściowych jest ściśle powiązany z ewolucją technologii półprzewodnikowej oraz rosnącymi wymaganiami dotyczącymi częstotliwości taktowania i integralności sygnału:

2.1 TTL (logika tranzystorowo-tranzystorowa) – od ok. 1964

TTL był jednym z pierwszych szeroko rozpowszechnionych standardów logiki cyfrowej i został wprowadzony przez Texas Instruments jako seria 7400. Oscylatory z wyjściem TTL pracują z napięciem zasilania 5 V i dostarczają zakresy poziomów bezpośrednio kompatybilne z bramkami TTL. Standard ten kształtował elektronikę cyfrową przez dziesięciolecia i był dominującym standardem logicznym aż do lat 90.

2.2 CMOS (Complementary Metal-Oxide-Semiconductor) – od ok. 1968

Technologia CMOS została pierwotnie opracowana dla złącz RCA (RCA) i charakteryzuje się wyjątkowo niskim poborem prądu w stanie spoczynku. Oscylatory CMOS generują sygnały wyjściowe typu rail-to-rail, co oznacza, że napięcie wyjściowe oscyluje niemal wyłącznie w zakresie od 0 V do Vcc. Wraz z postępującą miniaturyzacją i tendencją do stosowania niższych napięć zasilania (3,3 V, 2,5 V, 1,8 V), technologia CMOS stała się najszerzej stosowanym standardem wyjściowym dla oscylatorów.

2.3 Sinus – od początków techniki oscylatorów

Sinusoidalne sygnały wyjściowe są tak stare, jak sama technologia oscylatorów. Oscylatory fizycznie oscylują sinusoidalnie; wszystkie inne kształty sygnału są generowane przez obwody podłączone do urządzenia. Sygnały wyjściowe o przebiegu sinusoidalnym są preferowane w technologii wysokich częstotliwości, przyrządach pomiarowych i analogowym przetwarzaniu sygnałów, ponieważ nie generują harmonicznych.

2.4 Clipped Sine Wave – od ok. lat 70.

Wyjście Clipped Sine Wave stanowi kompromis między wyjściem sinusoidalnym a prostokątnym. Sygnał sinusoidalny jest ograniczany (clipowany) na szczytach, co tworzy bardziej strome zbocza niż przy czystym sinusie, ale mniej harmonicznych niż przy sygnale prostokątnym. Ten typ wyjścia znalazł zastosowanie szczególnie w telekomunikacji i w starszych aplikacjach wysokiej częstotliwości. Układy Clipped Sine Wave są dziś stosowane głównie jeszcze w TCXO. Dzięki tej technologii można budować znacznie bardziej energooszczędne TCXO niż z technologią CMOS. CSW-TCXO są dlatego stosowane jako referencja w urządzeniach nawigacyjnych, systemach alarmowych i bramkach. Wszędzie tam, gdzie potrzebny jest zasięg sygnału (radio) i bardzo dokładne pozycjonowanie.

2.5 LVPECL (Low-Voltage Positive Emitter-Coupled Logic) – od ok. lat 90.

Wraz z zapotrzebowaniem na coraz wyższe częstotliwości taktowania w systemach sieciowych i telekomunikacyjnych powstał LVPECL jako szybka różnicowa logika wyjściowa. LVPECL opiera się na klasycznej technice ECL (Emitter-Coupled Logic), opracowanej już w latach 60. dla zastosowań wysokoprędkościowych, i adaptuje ją do niższych napięć zasilania (3,3 V zamiast -5,2 V). LVPECL oferuje ekstremalnie krótkie czasy przełączania i jest odpowiedni dla częstotliwości znacznie powyżej 1 GHz.

2.6 LVDS (Low-Voltage Differential Signaling) – od 1994

LVDS został wprowadzony w 1994 roku jako standard ANSI/TIA/EIA-644 i optymalizuje różnicową transmisję sygnału pod kątem niskiego poboru prądu i wysokich szybkości transmisji danych. Niewielki różnicowy skok napięcia wynoszący zaledwie 350 mV umożliwia szybkie przełączanie przy minimalnej emisji elektromagnetycznej. LVDS jest dziś szeroko stosowany w interfejsach wyświetlaczy, połączeniach danych szeregowych i taktowaniu FPGA.

2.7 HCSL (High-Speed Current Steering Logic) – od ok. 2002

HCSL został opracowany specjalnie dla standardu PCI Express i od pierwszej generacji PCIe jest standardem zegara referencyjnego. PCI-SIG określił HCSL jako oparty na trybie prądowym sygnał różnicowy o bardzo niskim skoku napięcia, zoptymalizowany dla zegarów referencyjnych 100 MHz w systemach PCIe. HCSL jest dziś niezbędny w każdym PC, serwerze i systemie wbudowanym z interfejsem PCIe.

3. Przegląd kształtów sygnałów

Poniższe diagramy przedstawiają wyidealizowane przebiegi sygnałów siedmiu typów wyjściowych. Należy zwrócić uwagę na różne zakresy napięć i skoki sygnału – są one decydujące dla kompatybilności z następującymi odbiornikami.

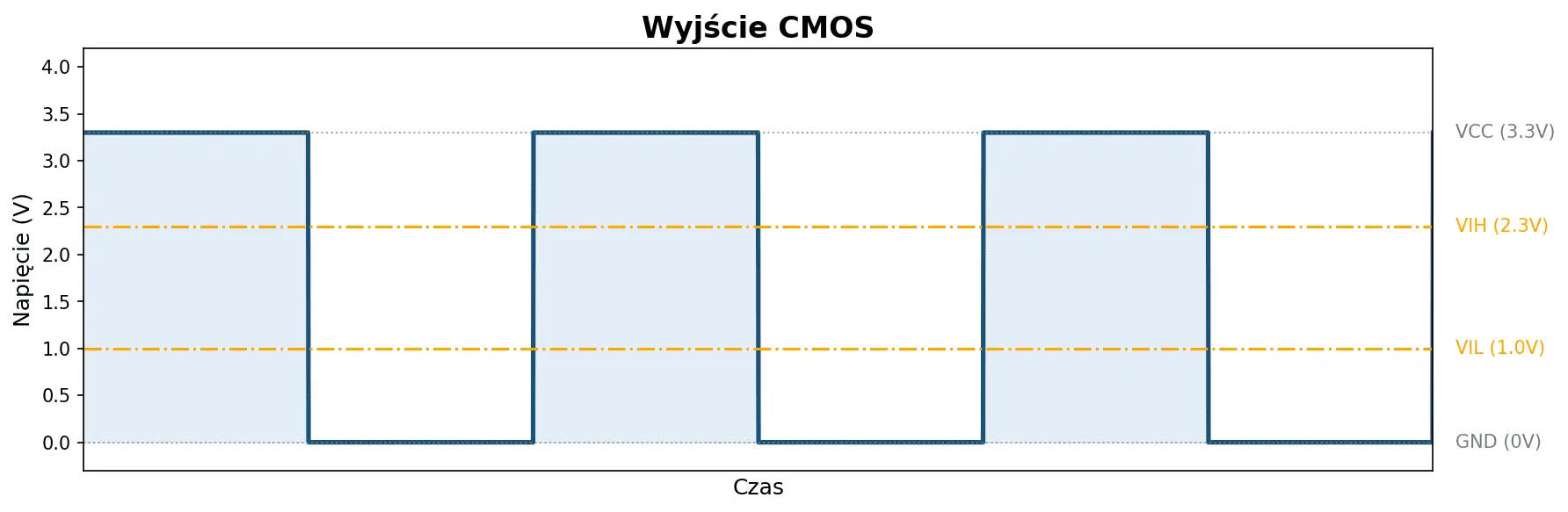

3.1 CMOS

Rys. 1: Sygnał wyjściowy CMOS – fala prostokątna rail-to-rail między 0 V a VCC (tutaj 3,3 V)

Sygnał CMOS charakteryzuje się pełnym skokiem napięcia między GND a VCC. Progi wejściowe VIL i VIH leżą typowo przy 30 % i odpowiednio 70 % VCC, co gwarantuje szeroki margines odporności na zakłócenia. Symetryczne struktury drivera wyjściowego (MOSFET kanału P/kanału N) umożliwiają niemal równe czasy narastania i opadania.

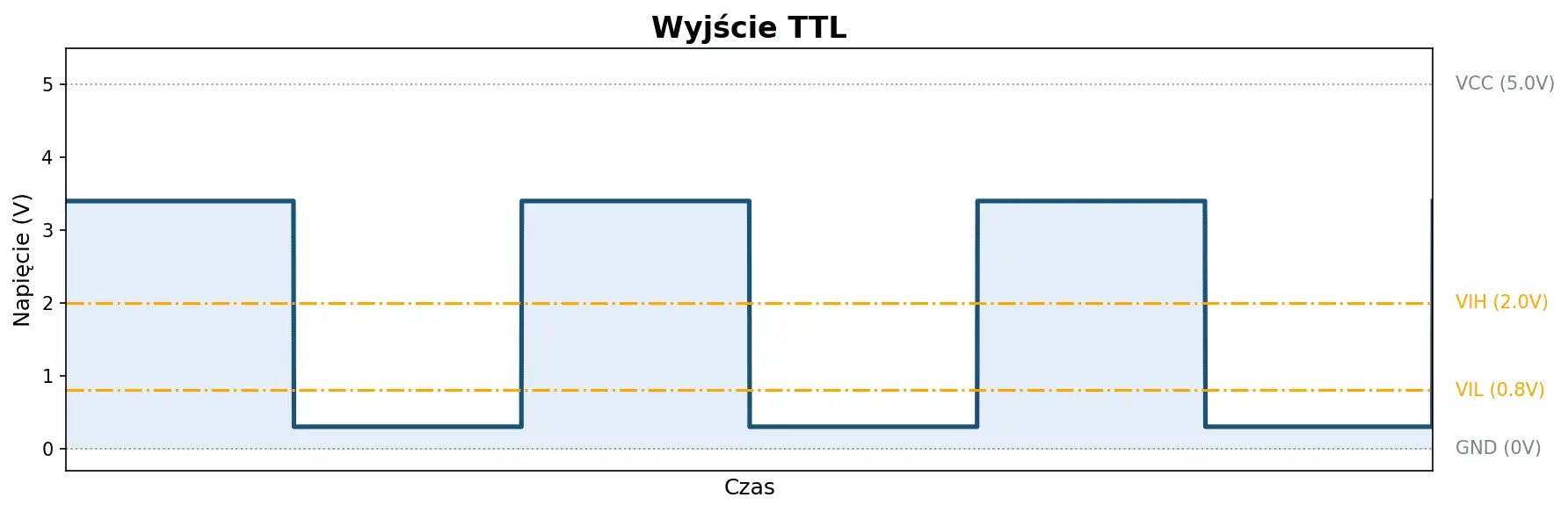

3.2 TTL

Rys. 2: Sygnał wyjściowy TTL – VOH typowo 3,4 V, VOL typowo 0,3 V przy zasilaniu 5 V

W przeciwieństwie do wyjścia CMOS, TTL nie osiąga poziomów rail-to-rail. Poziom wysoki (VOH) leży typowo przy 3,4 V (minimum 2,4 V), poziom niski (VOL) przy maksymalnie 0,4 V. Asymetryczne progi (VIL = 0,8 V, VIH = 2,0 V) wynikają z bipolarnej architektury tranzystorowej. Tzw. „strefa zabroniona“ między 0,8 V a 2,0 V nie może być przyjmowana w pracy statycznej.

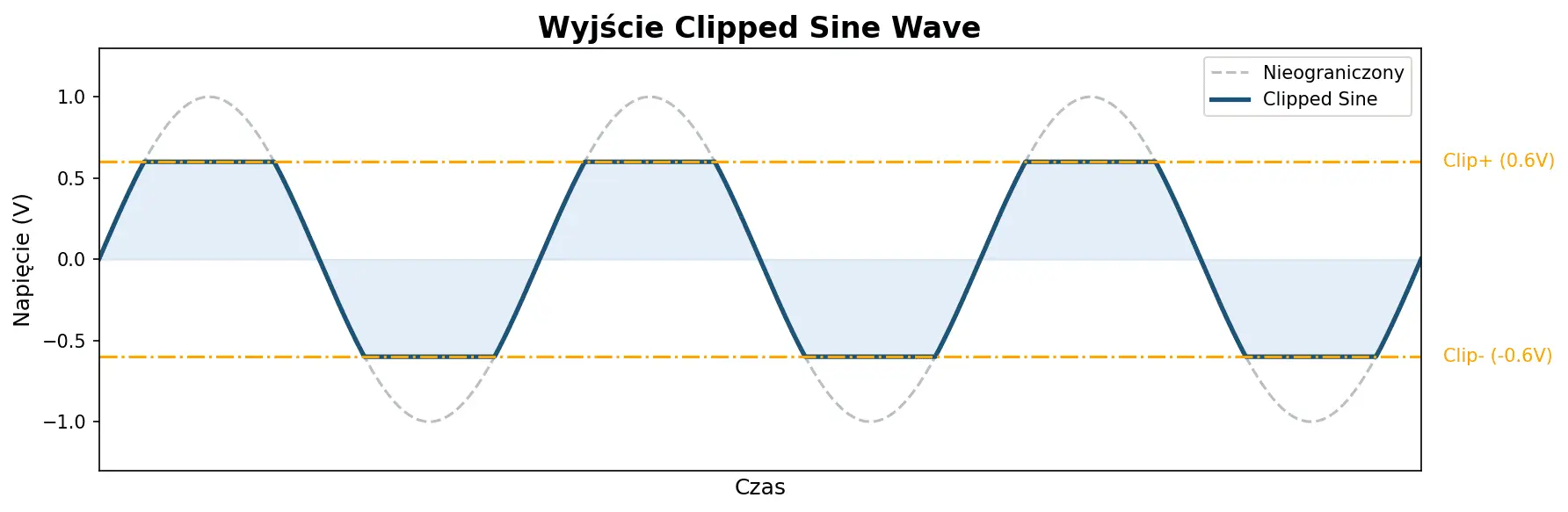

3.3 Clipped Sine Wave

Rys. 3: Wyjście Clipped Sine Wave – sygnał sinusoidalny z ograniczonymi szczytami amplitudy

W wyjściu Clipped Sine Wave naturalny sygnał sinusoidalny rezonatora kwarcowego jest ograniczany na zdefiniowanych progach. Linia przerywana pokazuje nieograniczony przebieg sinusoidalny. Dzięki clipowaniu powstają bardziej strome przejścia przez zero niż przy czystym sinusie, co ułatwia sterowanie następującą logiką, przy umiarkowanej zawartości harmonicznych.

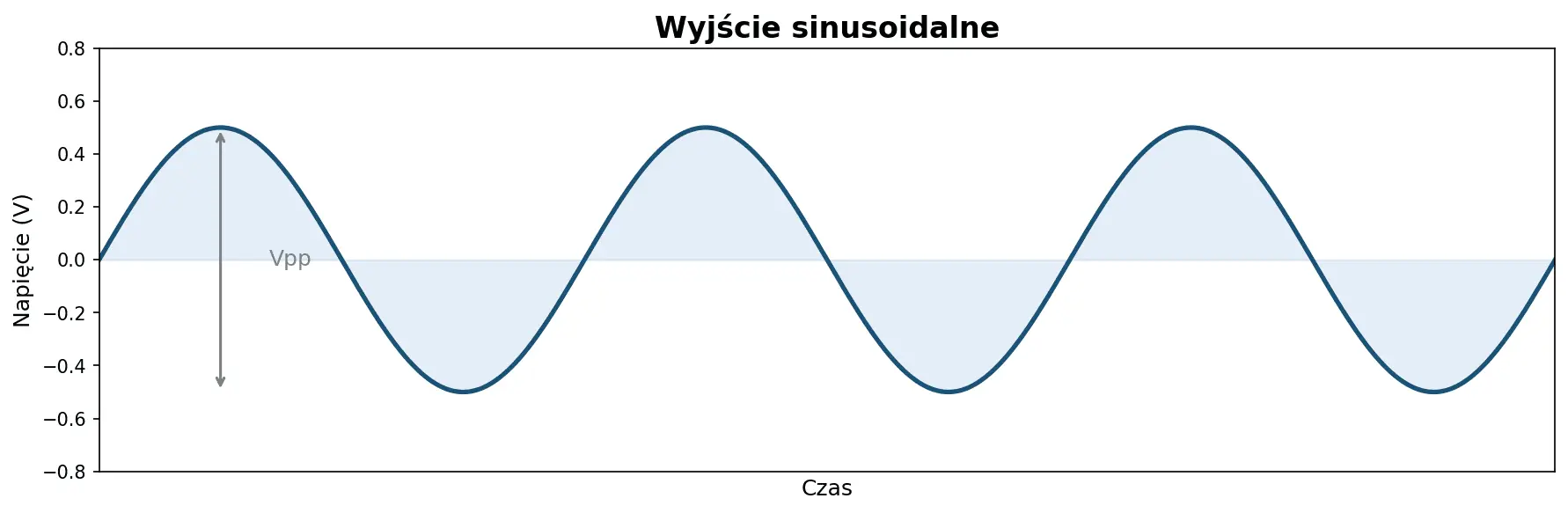

3.4 Sinus

Rys. 4: Wyjście sinusoidalne – czysty sygnał sinusoidalny ze zdefiniowaną amplitudą międzyszczytową (Vpp)

Wyjście sinusoidalne dostarcza najczystsze widmo ze wszystkich form wyjściowych: idealnie tylko jedną linię widmową przy częstotliwości podstawowej. Amplituda jest podawana jako napięcie międzyszczytowe (Vpp) lub jako moc w dBm. Typowe wartości wynoszą od 0,5 do 1,0 Vpp lub od 0 do +13 dBm w systemach 50 Ω.

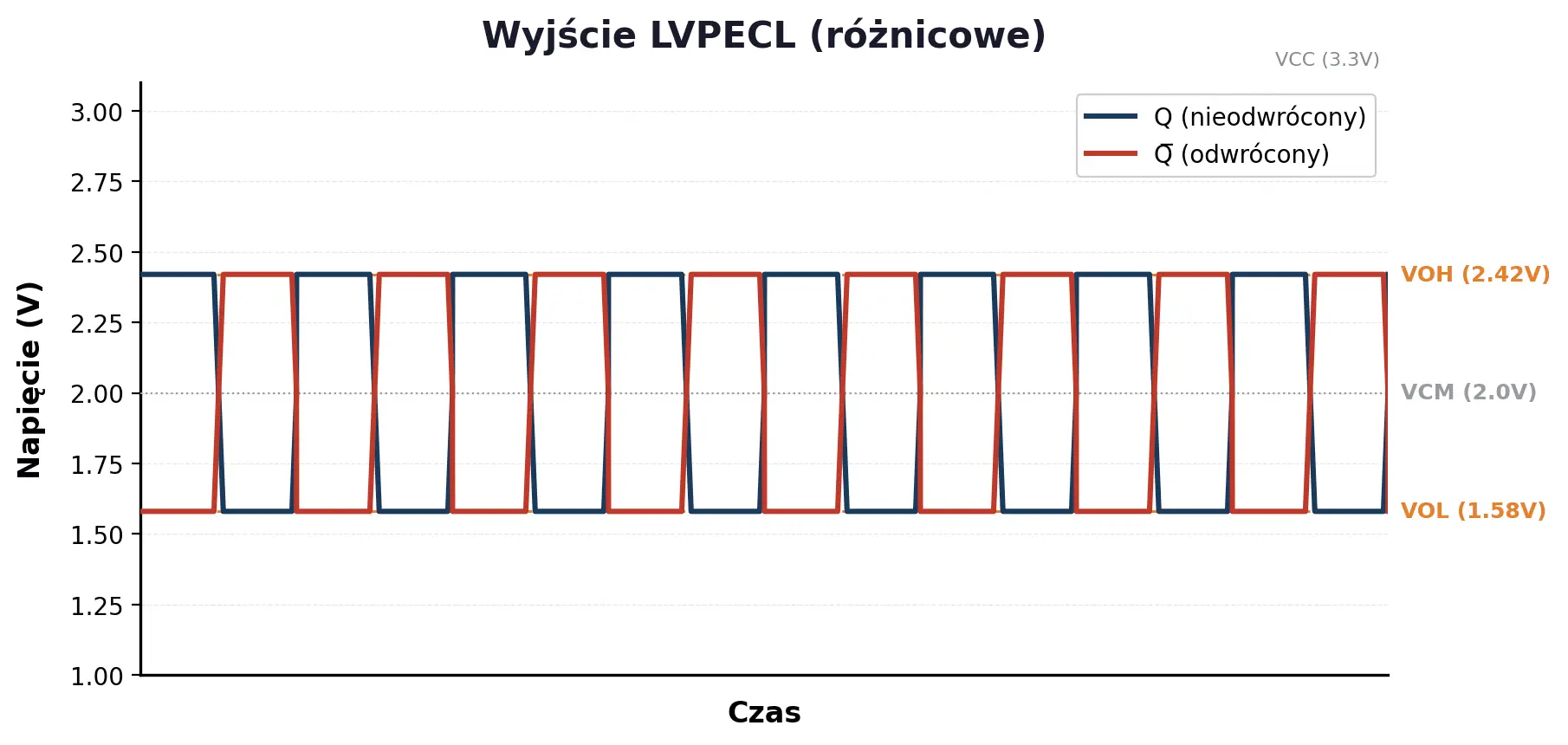

3.5 LVPECL

Rys. 5: Wyjście LVPECL – sygnał różnicowy z ca. 800 mV całkowitego skoku wokół VCC–1,3 V

LVPECL wykorzystuje różnicowe prowadzenie sygnału: dwa komplementarne wyjścia (Q i Q̅) przełączają się w przeciwfazie wokół wspólnego poziomu wspólnego (VCM), typowo przy VCC–1,3 V. Różnicowy skok napięcia wynosi ok. 800 mV. Architektura źródła prądowego umożliwia ekstremalnie szybkie czasy przełączania z minimalną tendencją do przerzutów.

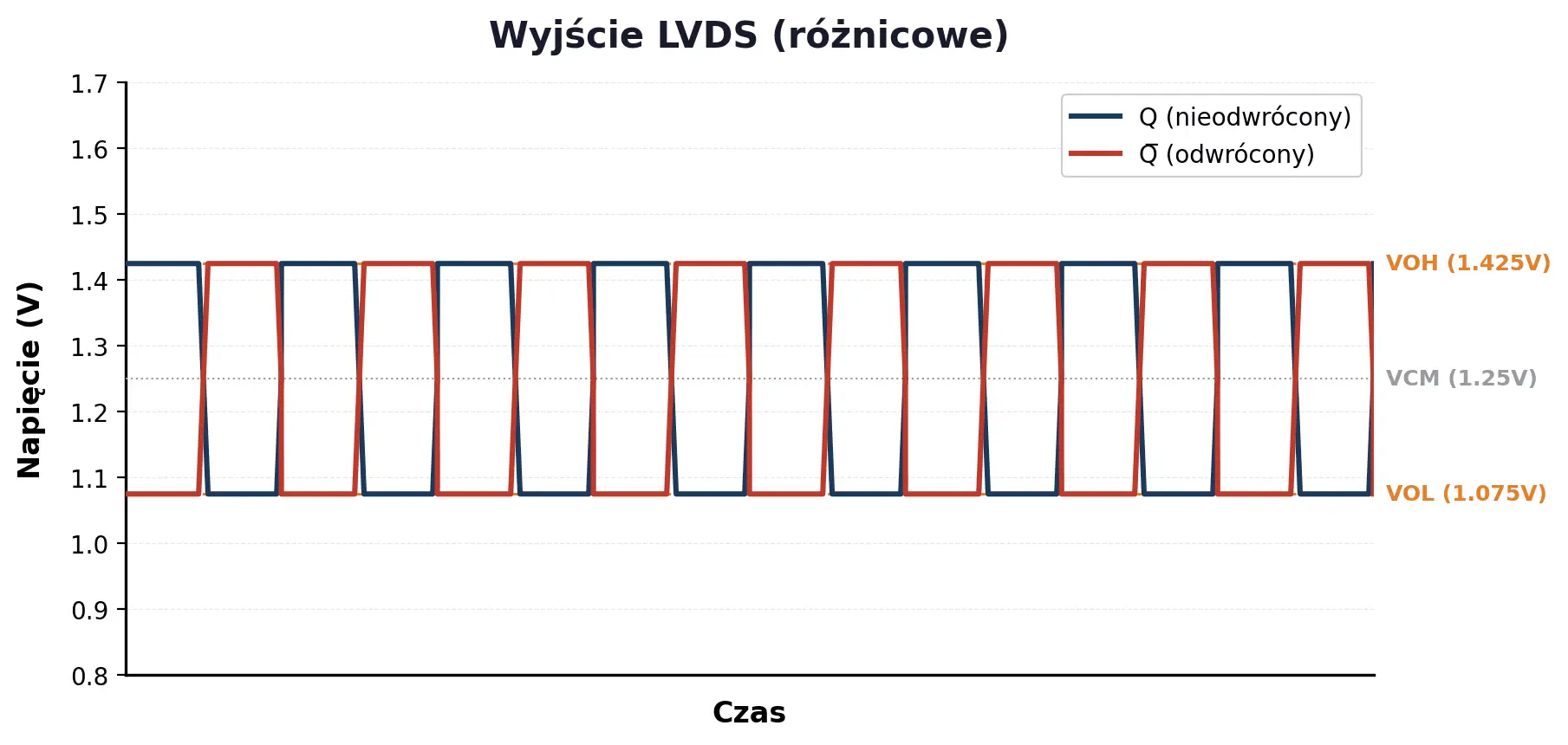

3.6 LVDS

Rys. 6: Wyjście LVDS – sygnał różnicowy z zaledwie 350 mV skoku wokół poziomu wspólnego 1,25 V

LVDS charakteryzuje się szczególnie niskim różnicowym skokiem napięcia wynoszącym zaledwie 350 mV. Poziom wspólny leży przy 1,25 V. Dzięki sterowanemu prądowo driverowi (typowo 3,5 mA) i terminacji 100 Ω osiągana jest wysoka integralność sygnału przy minimalnym poborze prądu. Niska amplituda minimalizuje emisję elektromagnetyczną.

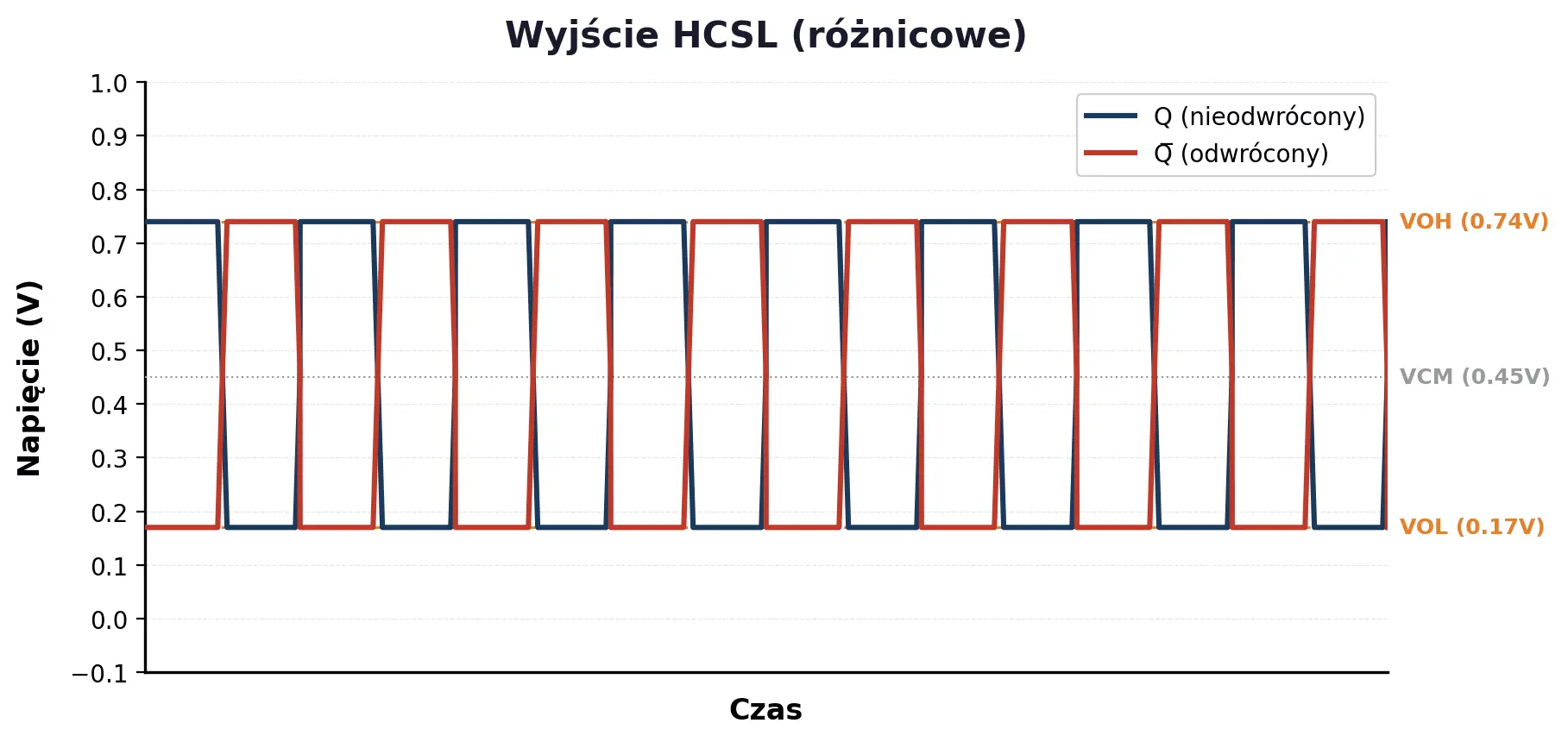

3.7 HCSL

Rys. 7: Wyjście HCSL – oparty na trybie prądowym sygnał różnicowy dla zegarów referencyjnych PCIe

HCSL pracuje z bardzo niskim skokiem napięcia: VOH leży typowo przy 0,74 V, a VOL przy 0,17 V, co daje poziom wspólny ok. 0,45 V. Architektura sterowania prądowego jest specjalnie zoptymalizowana pod kątem wymagań specyfikacji PCIe i umożliwia precyzyjne dopasowanie impedancji poprzez terminacje 50 Ω do masy.

4. Porównanie sygnałów wyjściowych

Poniższa tabela podsumowuje najważniejsze właściwości wszystkich siedmiu typów wyjściowych:

Typ | Typ sygnału | VCC (V) | VOH/ VOL (V) | Zróżnic. Skok | Maks. przybliżona częstotliwość | Typowe zastosowanie |

| CMOS | Single-ended | 1,8-5,0 | VCC/ 0 | - | ~285 MHz | Mikrokontrolery, FPGA, ogólna technika cyfrowa |

| TTL | Single-ended | 1,8-5,0 | 3,4/ 0,3 | - | ~150 MHz | Systemy legacy, sterowanie przemysłowe |

| Clipped Sine | Single-ended | 1,8/2,5/3,3 | zmienny | - | ~200 MHz | Telekomunikacja, zastosowania RF |

| Sinus | Single-ended | 3,3/5,0/12 | zmienny | - | >1 GHz | Technika RF, aparatura pomiarowa, synteza częstotliwości |

| LVPECL | Różnicowy | 2,5/3,3 | ~2,4/ ~1,6 | ~800 mV | >3 GHz | Sprzęt sieciowy, SONET/SDH, taktowanie szybkie |

| LVDS | Różnicowy | 2,5/3,3 | ~1,43/ ~1,07 | 350 mV | >1 GHz | Interfejsy wyświetlaczy, połączenia szeregowe, taktowanie FPGA |

| HCSL | Różnicowy | 3,3 | 0,74/ 0,17 | ~570 mV | ~200 MHz | Zegar referencyjny PCI Express (100 MHz) |

5. Istotne różnice w szczegółach

5.1 Single-Ended vs. różnicowy

Najbardziej fundamentalną różnicą między typami wyjść jest prowadzenie sygnału. CMOS, TTL, Clipped Sine Wave i Sinus to sygnały single-ended – odnoszą się do wspólnej masy. LVPECL, LVDS i HCSL natomiast to sygnały różnicowe z dwiema komplementarnymi liniami. Sygnały różnicowe oferują decydujące zalety przy wyższych częstotliwościach: tłumią zakłócenia wspólne, umożliwiają mniejsze skoki napięcia i dzięki temu szybsze czasy przełączania przy mniejszej emisji elektromagnetycznej.

5.2 Skok napięcia i margines odporności na zakłócenia

CMOS oferuje ze swoim wyjściem rail-to-rail największy bezwzględny skok napięcia, a tym samym najlepszy statyczny margines odporności na zakłócenia. TTL ma przez asymetryczne poziomy bardziej ograniczony margines. Standardy różnicowe (LVPECL, LVDS, HCSL) kompensują swoje mniejsze skoki napięcia poprzez tłumienie składowej wspólnej transmisji różnicowej, dzięki czemu w zakłóconych środowiskach często pracują niezawodniej niż sygnały single-ended.

5.3 Pobór prądu

Oscylatory CMOS w stanie statycznym pobierają niemal zero prądu; pobór rośnie proporcjonalnie do częstotliwości (dynamiczna strata mocy). TTL ma stałe wyższe zużycie prądu spoczynkowego z powodu architektury bipolarnej. LVPECL wymaga zewnętrznych rezystorów terminujących i ma najwyższy pobór prądu spośród standardów różnicowych. LVDS jest znany z niskiego poboru prądu (typowo 3,5 mA prądu drivera). HCSL znajduje się pod względem poboru prądu między LVDS a LVPECL.

5.4 Zakres częstotliwości i główne obszary zastosowań

W przypadku częstotliwości do około 200 MHz, oscylatory CMOS są w większości przypadków pierwszym wyborem ze względu na ich wszechstronność, prostą konstrukcję i powszechną dostępność. Powyżej około 200 MHz zalecane są wyjścia różnicowe. LVPECL oferuje najwyższe częstotliwości (>3 GHz) i jest stosowany w urządzeniach sieciowych i telekomunikacyjnych. LVDS obejmuje szeroki zakres średnich częstotliwości i jest szczególnie popularny w układach FPGA i wyświetlaczach. HCSL jest zoptymalizowany pod kątem niszowego zastosowania: zegara referencyjnego 100 MHz dla PCI Express.

5.5 Terminacja i złożoność układu

Wyjścia CMOS i TTL z reguły nie wymagają zewnętrznej terminacji przy krótkich ścieżkach – to czyni je szczególnie prostymi w zastosowaniu. LVPECL wymaga obowiązkowo zewnętrznych rezystorów terminujących (typowo: terminacja Thévenin do VCC–2 V lub rezystory do masy), co zwiększa złożoność układu. LVDS jest standardowo terminowany rezystorem różnicowym 100 Ω przy odbiorniku. HCSL używa rezystorów 50 Ω do masy na każdym wyjściu.

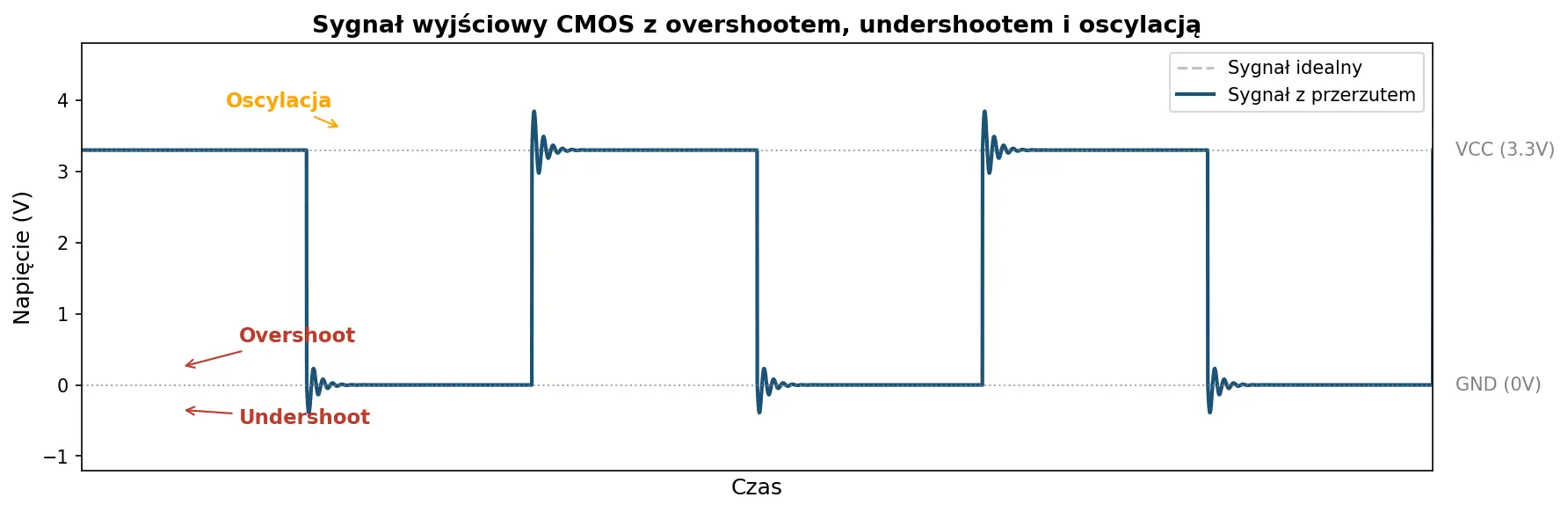

6. Przerzuty w sygnałach wyjściowych oscylatorów

6.1 Czym są przerzuty?

Przekroczenie i niedokroczenie to krótkie skoki napięcia występujące podczas szybkich operacji przełączania. Przy zboczu narastającym napięcie chwilowo przekracza VCC (przekroczenie), natomiast przy zboczu opadającym spada nieznacznie poniżej GND (niedokroczenie). Po tych skokach często następują tłumione oscylacje, zwane „dzwonieniem”.

Przyczyna leży w połączeniu bardzo stromych zbocz przełączających drivera wyjściowego z pasożytniczymi indukcyjnościami i pojemnościami ścieżki, obudowy i pojemności obciążenia. Fizycznie powstaje obwód rezonansowy z indukcyjności linii i pojemności wejściowej odbiornika. Im bardziej strome zbocze i im dłuższa ścieżka, tym silniejszy przerzut.

6.2 Dlaczego przerzuty są problematyczne?

Przerzuty przekraczające VCC lub spadające poniżej GND mogą wprowadzić diody ochronne ESD układu odbiorczego w przewodzenie i generować prądy pasożytnicze. W najgorszym przypadku może to doprowadzić do latch-up – niekontrolowanego przepływu prądu przez pasożytnicze struktury tyrystorowe w układzie CMOS, który może zniszczyć komponent. Silny ringing może ponadto powodować wielokrotne wyzwalanie na wejściach zegarowych, gdy napięcie wielokrotnie przekracza próg przełączania, co prowadzi do błędnego działania systemu.

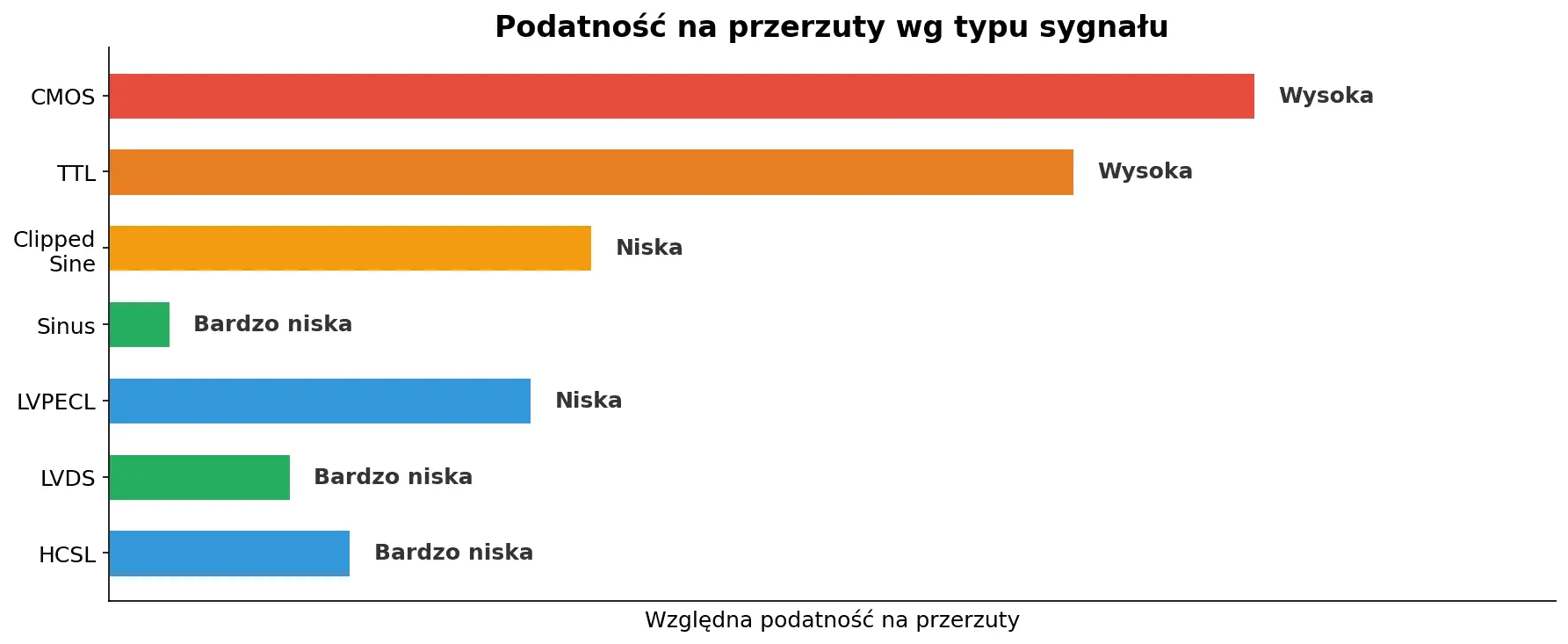

6.3 Zestawienie: przerzuty wg typu sygnału

Podatność na przerzuty różni się znacznie między poszczególnymi typami wyjściowymi. Poniższy wykres pokazuje względną podatność w porównaniu:

6.4 Przerzuty w sygnałach single-ended

CMOS: Najbardziej narażony. Symetryczne drivery MOSFET kanału P/N generują bardzo strome zbocza, które w połączeniu z indukcyjnościami ścieżek powodują wyraźne przerzuty. Szczególnie w przypadku nowoczesnych niskonapięciowych oscylatorów CMOS (1,8 V) przerzuty mogą być znaczące w stosunku do napięcia zasilania.

TTL: Również podatny, choć z nieco innych powodów. Asymetryczny stopień wyjściowy totem-pole generuje krótki impuls prądowy przy zboczu narastającym, gdy oba tranzystory jednocześnie przewodzą (cross-conduction). Typowo nieco wolniejsze zbocza w porównaniu z nowoczesnym CMOS nieco łagodzą problem.

Clipped Sine Wave: Znacznie mniej podatny. Ograniczone szczyty amplitudy i stosunkowo łagodne zbocza wytwarzają znacznie mniej energii wysokoczęstotliwościowej, która mogłaby wzbudzić odbicia i ringing. Clipping działa jak naturalne ograniczenie amplitudy, które tłumi przerzuty już w samym sygnale.

Fala sinusoidalna: Praktycznie odporna na klasyczne przeregulowanie. Ponieważ sygnał nie zawiera gwałtownych przejść krawędzi, nie jest generowany szerokopasmowy impuls energetyczny, który mógłby wzbudzić rezonanse linii. Jednak niedopasowanie impedancji może prowadzić do fal stojących i odbić, które zmieniają amplitudę sygnału w niektórych punktach. Jest to kontrolowane przez klasyczną terminację RF (terminacja 50 Ω lub 75 Ω).

6.5 Przerzuty w sygnałach różnicowych

LVPECL: Dzięki stopniowi wyjściowemu źródła prądowego inherentnie dobrze tłumiony. Sterowanie prądowe ogranicza maksymalną stromość zbocz w naturalny sposób. Przy niewystarczającej terminacji mogą jednak wystąpić odbicia, ponieważ LVPECL pracuje na bardzo wysokich częstotliwościach. Prawidłowy układ Thévenin lub wtornik emiterowy jest tu decydujący – nie przede wszystkim z powodu przerzutów, lecz aby zapewnić prawidłowy punkt pracy i uniknąć odbić.

LVDS: Bardzo wytrzymały konstrukcyjnie. Sterowany prądowo driver dostarcza stały prąd typowo 3,5 mA do terminacji różnicowej 100 Ω, co fizycznie ogranicza skok napięcia. Nawet przy nieciągłościach impedancji odbicia pozostają niewielkie, ponieważ mały skok napięcia wynoszący zaledwie 350 mV dostarcza mało energii do zakłóceń. LVDS jest jednym z najbardziej wyrozumiałych standardów pod względem integralności sygnału.

HCSL: Zachowuje się podobnie do LVDS dzięki architekturze opartej na prądzie. Bardzo niski skok napięcia i terminacja 50 Ω do masy zapewniają czyste dopasowanie impedancji. W specyfikacji PCIe dopuszczalne przerzuty są jawnie zdefiniowane i ściśle tolerancjonowane, tak że oscylatory zgodne z HCSL inherentnie spełniają te wymagania.

Środki zaradcze w celu kontroli przerzutów

Najskuteczniejszym środkiem w przypadku sygnałów single-ended (w szczególności CMOS i TTL) jest rezystor szeregowy bezpośrednio na wyjściu oscylatora, typowo w zakresie od 22 do 47 Ω. Rezystor ten tworzy wraz z impedancją ścieżki dzielnik napięcia, który tłumi zbocze i absorbuje odbicia. Optymalna wartość wynika z różnicy między impedancją ścieżki a impedancją wyjściową drivera.

Ponadto pomagają krótkie ścieżki o kontrolowanej impedancji, minimalizacja przelotków (via) na linii zegara, ciągła płaszczyzna masy pod linią sygnałową oraz wystarczające kondensatory odsprzęgające w pobliżu oscylatora (typowo 100 nF ceramicznych plus 10 µF). Niektórzy producenci oscylatorów CMOS oferują ponadto modele z kontrolowaną stromością zbocz (Slew Rate Control), które łagodzą problem już w driverze.

W przypadku sygnałów różnicowych (LVPECL, LVDS, HCSL) prawidłowa, zgodna ze specyfikacją terminacja jest najważniejszym środkiem. Ponadto obie linie pary różnicowej powinny być zawsze prowadzone z jednakową długością i ciasnym sprzężeniem, aby zminimalizować skew (różnice czasów propagacji) i zachować tłumienie składowej wspólnej.

7. Pomoc decyzyjna

Wybór właściwego typu wyjścia zależy zasadniczo od czterech czynników: wymaganej częstotliwości taktowania, rodziny logicznej odbiornika, dostępnego budżetu mocy i wymagań dotyczących integralności sygnału.

Przypadek zastosowania | Zalecenie |

| Ogólna technika cyfrowa, µC, FPGA-I/O (do ~200 MHz) | CMOS – Najprostsze i najtańsze rozwiązanie, rail-to-rail, najszersza dostępność, elastyczne napięcie zasilania (1,8–5,0 V) |

| Systemy legacy 5V, sterowanie przemysłowe | TTL – Bezpośrednio kompatybilny ze starszymi rodzinami logicznymi 5V; coraz częściej zastępowany przez CMOS z zasilaniem 5V |

| Zastosowania RF, układy z transformatorem | Clipped Sine Wave lub Sinus – Niższa zawartość harmonicznych zmniejsza problemy EMC i umożliwia precyzyjną syntezę częstotliwości |

| Sprzęt sieciowy o dużej prędkości (>622MHz) | LVPECL – Najwyższa prędkość przełączania, idealny dla SONET/SDH, Ethernet-PHY i zegarów backplane |

| Taktowanie FPGA, szeregowa transmisja danych, interfejsy wyświetlaczy | LVDS – Optymalny kompromis między prędkością, poborem prądu i zachowaniem EMC |

| Zegar referencyjny PCI Express | HCSL – Jedyny standard zegarowy określony przez PCI-SIG dla systemów PCIe |