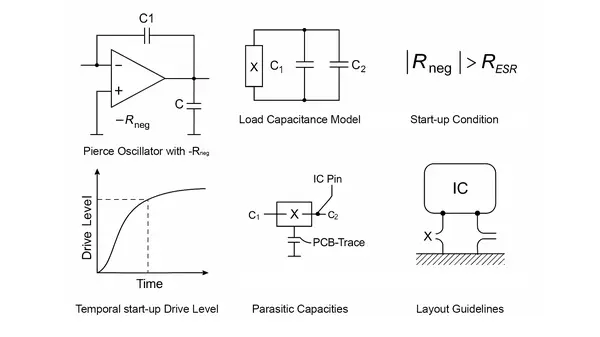

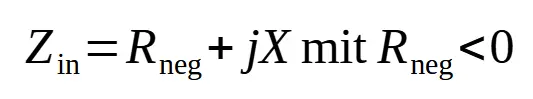

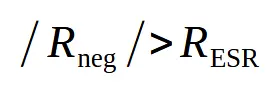

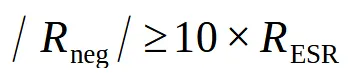

Oznacza to, że wartość ujemnej rezystancji wejściowej musi być większa niż rezystancja szeregowa (ESR) kryształu.

Tylko wtedy wystąpi wzmocnienie netto prowadzące do oscylacji.

F.2: Wpływ na bezpieczeństwo reakcji przejściowej

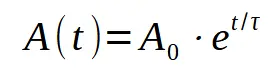

Jeśli wartość ujemnej rezystancji wejściowej jest zbyt mała (tj. -Rneg jest zbyt słaba), dzieje się co następuje:

- Kwarc otrzymuje zbyt mało energii → powolne oscylacje lub brak oscylacji w ogóle

- Oscylacja rozpoczyna się dopiero przy wyższym napięciu zasilania lub temperaturze

- Rozruch w trybach pracy o niskim poborze mocy staje się zawodny.

Typowa przyczyna:

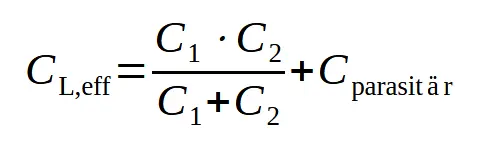

Niektóre nowoczesne MCU mają słabe wzmacniacze oscylatora ze względu na wydajność, co oznacza, że -Rneg jest mniejszy niż w starszych generacjach układów scalonych. Jednocześnie, wiele konstrukcji pracuje z małymi pojemnościami obciążenia lub długimi ścieżkami, co zwiększa straty pasożytnicze.

P.3: Dlaczego kryształy o niskim ESR są szczególnie ważne?

Współczynnik ESR kryształu określa jego straty wewnętrzne. Niski współczynnik ESR oznacza

- niższe straty

- niższe konieczne przeciwwzmocnienie

- wysoką stabilność przejściową nawet przy słabych stopniach oscylatora

- krótszy czas rozruchu

- Bardziej stabilna oscylacja w zależności od temperatury

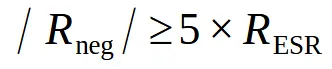

Zalecenia praktyczne:

- Należy używać kryształów, których ESR jest znacznie poniżej maksymalnej wartości określonej przez układ scalony.

- Jeśli mikrokontroler określa maksymalny ESR na poziomie 70 Ω, idealnym rozwiązaniem jest kryształ o ESR 30-50 Ω. Pozostawia to wystarczający margines bezpieczeństwa przed potencjalnie niską ujemną rezystancją wejściową oscylatora.

F.4: Wnioski dotyczące interakcji -Rneg i ESR kwarcu

Niezawodność odpowiedzi przejściowej zależy zasadniczo od następujących czynników:

- wewnętrzny oscylator zapewnia wystarczającą ujemną rezystancję wejściową,

- kryształ ma wystarczająco niską ESR,

- pojemności obciążenia są prawidłowo zwymiarowane.

Tylko wtedy, gdy stosunek -Rneg do ESR jest prawidłowy, kryształ uruchomi się szybko, niezawodnie i w całym zakresie temperatur i napięć.